What is eFPGA?

1、 Introduction to eFPGA

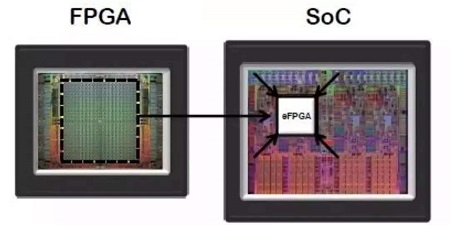

EFPGA (Embedded FPGA) embeds one or more FPGAs into chips such as ASICs, ASSPs, or SoCs in the form of IPs. This IP can be licensed for use similar to other IPs used in semiconductor design.

In other words, eFPGA is a digitally reconfigurable structure composed of programmable logic in programmable interconnections, typically represented as a rectangular array with data inputs and outputs located around edges. EFPGA typically has hundreds or thousands of inputs and outputs and can be connected to buses, data paths, control paths, GPIO, PHY, or any desired device.

Why has eFPGA attracted so much attention? There are two main points: firstly, with the emergence of each generation of new processes, development costs are rapidly increasing. This is driven by the complexity of abstract design itself and the physical implementation of these designs in actual SoC devices, including software tools, engineering time, and mask costs. Secondly (and vice versa), the cost per unit function of these devices has been decreasing. For example, 20 to 30 years ago, FPGA gates were relatively expensive, so FPGA devices were often used for prototype design and pre production, rather than large-scale production applications. Therefore, previous attempts to add FPGA gates to ASICs often increased overall chip size and complexity, resulting in new hybrid devices becoming too expensive to implement.

The high cost involved in SoC design increases the risk associated with the lack of suitable products to meet specific market demands, while the relatively low cost of FPGA gates means that embedding FPGA technology can achieve a certain degree of design flexibility (thereby reducing market risks), which is economically meaningful.

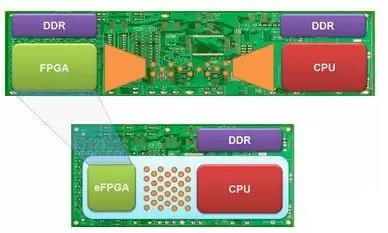

Unlike the design process of independent FPGAs, eFPGA designers can choose the exact amount of logic, DSP, and memory resources required by customer applications. When entering mass production, eFPGA can also reduce system costs, power consumption, and board space by eliminating independent FPGAs.

2、 The advantages of eFPGA

Compared to FPGA, eFPGA has the following advantages.

Higher performance: eFPGA connects to ASICs through a wide range of parallel interfaces, providing higher throughput and latency measured in single bit clock cycles.

Low power consumption: Programmable I/O circuits account for half of the total power consumption of independent FPGAs. EFPGA has a direct wired connection to SoC, completely eliminating large programmable I/O buffers. The size of eFPGA can accurately meet your needs, and you can adjust the processing technology to balance performance and power consumption.

Lower system cost: The core size of eFPGA is much smaller than that of independent FPGA, eliminating programmable I/O buffers, unused DSP and memory module, and over configured LUTs and registers. Traditional FPGAs have a large number of pins and small pin spacing, so it is necessary to build multi-layer PCBs. Embedded FPGA eliminates the need for dedicated PCBs and all supporting components, such as power regulators, clock generators, level converters, and passive components.

Higher system reliability and yield: Integrating FPGA functions into ASICs can improve system level signal integrity and eliminate reliability and yield losses associated with installing independent FPGAs on PCBs.

EFPGA is now available from multiple suppliers, various foundries (TSMC, Lattice, SMIC International, and Samsung), and process nodes (such as 180, 40, 28, 22, 16, 14, 12, and 7nm).

Until today, the concept of eFPGA has been widely accepted in the industry, and the number of companies in this field is gradually increasing.

FlexLogix Compa

FlexLogix is a pioneer in eFPGA, providing solutions for building flexible chips and accelerating neural network inference. Its eFPGA platform enables chips to flexibly handle constantly changing protocols, standards, algorithms, and customer needs, and enables reconfigurable accelerator pedals that can accelerate critical workloads by 30 to 100 times compared to processors.

Fast Logic

QuickLogic is a mature FPGA supplier focused on developing low-power, multi-core semiconductor platforms and intellectual property ("IP") for artificial intelligence ("AI"), voice, and sensor processing. Its main market is the ultra-low power SoC market, such as Bluetooth, the Internet of Things, and so on. Its eFPGA will bring configurability to these ultra-low power SoCs, resulting in better power and cost. In addition, QuickLogic's eFPGA support for SMIC International, known for its cost-effectiveness, is also a major highlight.

Menta Company

Menta is the only remaining eFPGA supplier in Europe. It is the only validated programmable logic supplier in Europe that can embed its IP into customer SoC and ASIC. This programmable logic takes the form of an embedded FPGA IP. It provides customers with the possibility of extracting a small portion from their SoC and owning it

SoC and enable it to implement a low-power FPGA that can be programmed by them or on-site customers.

Nano Xplore

NanoXplore is a company headquartered in France. The company is a pioneer in designing large-scale programmable logic arrays for the most advanced FPGA cores. NanoXplore provides advanced silicon validated eFPGA IP at leading foundries, supporting up to 28nm of validated technology. NanoXplore has also developed a highly innovative electronic device diagnostic technology called silicon rating.

Adidas

ADICSYS is a fabless semiconductor company that designs and licenses soft FPGA IPs for ASICs and SOC. These programmable kernels can easily be fully integrated into the user's RTL design process. ADICSYS has accumulated over ten years of experience in customizing FPGA and eFPGA projects, as well as leading semiconductor products. Like other IPs, the unique opportunity to include FPGA functionality in ASICs brings the flexibility required to modify functionality without the need to redesign chips or allow devices to meet a wide range of application requirements. In both cases, better control of NRE and TTM is possible.

Effeni

Efinix is an innovator in programmable product platforms and technologies. The company's Quantum programmable technology enables advanced programmable chip products in the fields of ASIC, ASSP, and FPGA. With Quantum's power performance advantages, the Infinix products meet the needs of high capacity, low power consumption, and small-sized products. EFINIX's joint development activities focused on infrastructure, data centers, and advanced silicon processes have further expanded the company's leadership position in the programmable industry.

In the era of scarce semiconductor startups, these eFPGA startups are growing exponentially. Companies such as Flex Logix and Menta have already made significant investments, while companies such as Acronix and QuickLogic have made significant investments in eFPGA based on internal growth expectations.

4、 Common Questions about eFPGA

Can eFPGA run at the frequency required for my design?

Compared to ASICs, most FPGA designs do not operate at the same frequency. In fact, FPGA cannot win at high clock frequencies. The high performance of FPGA is mainly achieved through its extremely high hardware parallel processing ability, deep pipeline, and high bit wide bus.

Embedded FPGAs, also known as eFPGAs, are essentially programmable logic arrays, so they cannot compete with ASICs solely in terms of operating frequency.

However, the industry and academia are constantly researching methods to break through FPGA frequency limitations. For example, Intel has adopted the HyperFlex architecture in its next-generation high-end FPGA product Stratix10, which introduces multiple register arrays between programmable logic units, which can increase the FPGA's running speed by 1.5 to 2 times.

Introduction of multiple register arrays into programmable logic units

Many application scenarios have high tolerance for errors, so simple "overclocking" of FPGAs can greatly improve their performance at the cost of a small probability of accuracy loss.

Will the power consumption of eFPGA be too high?

The answer to this question should be no. Moreover, the power density of eFPGA is usually much lower than other IPs on FPGA or ASIC and SoC.

For traditional FPGAs, one of the main "power consumption" is the programmable I/O part of the FPGA. The eFPGA is directly connected to another IP of the ASIC through an on chip bus, which directly removes the I/O part of the original FPGA, thereby reducing most of the power consumption.

On the other hand, as mentioned in the previous question, the frequency of eFPGA is much lower than other IPs on ASICs or SoCs, which makes the dynamic power consumption of eFPGA relatively low.

Can eFPGA provide sufficient bandwidth for my design?

For traditional FPGA designs, system performance is often directly limited by the number of I/O pins on the FPGA chip. Especially for many communication, network, and high-performance computing applications, FPGA chips need to provide a large number of high-performance SerDes transceivers and universal I/O pins for data exchange and transmission to external systems, which is usually limited by chip packaging technology.

In contrast, eFPGA has no pin count limit because it is essentially an IP core integrated into an ASIC. Therefore, compared to FPGA, the communication bandwidth between eFPGA and ASIC or SoC can be increased by more than 10 times. In fact, this is one of the main driving factors for creating and using eFPGA.

Electronic Programmable Gate Array

EFPGA is not a chip to chip connection, but directly communicates through different IPs on the chip, which greatly increases communication bandwidth and reduces communication latency.

4. Will using eFPGA cause excessive chip area?

When ASIC or SoC engineers first see an FPGA, they are usually shocked by the size of the FPGA chip, as it is usually too large.

Generally speaking, half of the main chip area of an FPGA is programmable logic units, and the other half is programmable sequential I/O and related circuits. Programmable I/O is one of the assets of FPGA, which allows them to communicate with almost any other chip or system, including microprocessors, ASICs, memory, and other FPGAs. This is why the chip area of the programmable I/O part is so large.

Compared to FPGA, eFPGA does not require the implementation of programmable I/O components, as the ASIC IP that communicates with eFPGA is fixed during design. When the programmable I/O part is removed, the chip area of eFPGA is greatly reduced for the same FPGA logic density.

Will the cost of using eFPGA be high?

Acronix is one of the leading providers of eFPGA, and its Vice President of Marketing, Steve Mensor, stated that the cost of using eFPGA is "not more expensive than other IPs"

Cost of use should be viewed from two perspectives. The first is the direct monetary cost of the user, which is the funds paid for the chip or IP. The other is the diversity of functions that the purchased IP can provide, which means that the cost of implementing a certain function is shared. For FPGA or eFPGA, their most powerful feature is the ability to implement different user logic and modify functional logic after chip flow, significantly reducing the development risk of SoC and ASIC and increasing design flexibility.

-

Whatsapp